معماری وفقی آشکارساز اسپایک با ویولت برای مرتب سازی اسپایکهای نورونی در FPGA

Adaptive Spike Detector Architectures with Wavelet for Online Neural Spike Sorting on FPGA

نویسندگان :

پیام پاکروان ( دانشگاه تهران ) , پدرام پاکروان ( دانشگاه امام حسین (ع) )

چکیده

The extracellular recording system has been extensively used in different fields ranging from fundamental neuroscientific research to clinical usages. Spike detection is a basic step in the online neural spike sorting for the decomposition of neural recordings. However, in the spike sorting system, how to accurately detect spikes from the signal acquisition system in real-time is yet the main incentive function. also, the common difficulty in Brain-Machine Interface (BMI) is the Changes in neural signals over time, which require training again. However, repeated training is not appropriate in true use reason. We used the wavelet transform coefficients as method spike detection in neural recordings, versus to adaptive amplitude threshold system. This paper presents a simple front-end circuit for detecting action potentials (AP) in extracellular neural recordings. By implementing a real-time, adaptive algorithm to specify an efficient threshold for robust spike detection. Threshold value online with supervision the standard deviation of wavelet coefficients, the suggested detector can adaptively fix for every channel separately without need user interposition. The characteristics and implementation result of the designed spike sorting system on a Xilinx Spartan-6 XC6SLX9 field-programmable gate array (FPGA) are presented. The archetype tetrode spike detector was implemented and tested in an FPGA. This method provides spike detection with almost 90% accuracy even until the signal-to-noise ratio (SNR) is low.کليدواژه ها

Adaptive Threshold, Hardware Architectures SWT, Moving Standard Deviation, Spike Sortingکد مقاله / لینک ثابت به این مقاله

برای لینک دهی به این مقاله، می توانید از لینک زیر استفاده نمایید. این لینک همیشه ثابت است :نحوه استناد به مقاله

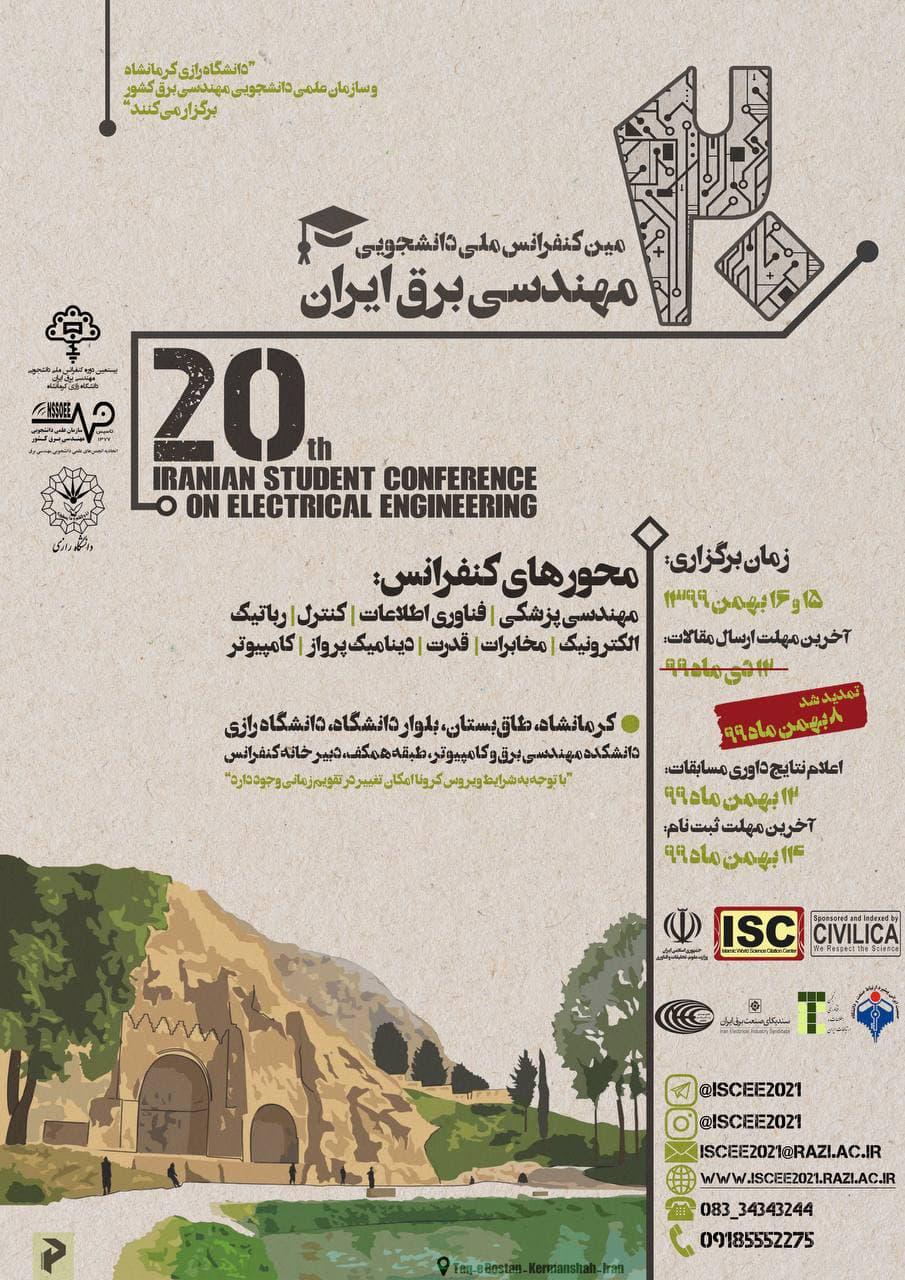

در صورتی که می خواهید در اثر پژوهشی خود به این مقاله ارجاع دهید، به سادگی می توانید از عبارت زیر در بخش منابع و مراجع استفاده نمایید:پیام پاکروان , 1400 , معماری وفقی آشکارساز اسپایک با ویولت برای مرتب سازی اسپایکهای نورونی در FPGA , بیستمین کنفرانس ملی دانشجویی مهندسی برق ایران

دیگر مقالات این رویداد

© کلیه حقوق متعلق به دانشگاه رازی کرمانشاه میباشد.