طراحی تثبیت کننده ولتاژ با افت کم دیجیتالی با استفاده ازثبات تقریب متوالی ادغام شده با شمارندهی بالا-پایین شمار

Design of Digital Low-Dropout Voltage Regulator using Successive Approximation Register embedded with Up-Down Counter

نویسندگان :

شهباز ریحانی ( دانشگاه گیلان ) , ساناز سعیدپور ( دانشگاه گیلان )

چکیده

در این مقاله یک تثبیت کننده با افت ولتاژ کم (Low-Dropout) دیجیتالی با استفاده ازثبات تقریب متوالی (Successive Approximation Register) ادغام شده با شمارندهی بالا-پایین شمار (Up-Down Counter) طراحی شده است. در این طراحی از سه مقایسه گر برای مقایسه ی ولتاژ خروجی با ولتاژ مرجع, استفاده شده است. لذا برای ولتاژ مرجع حد مجاز بالا و حد مجاز پایین در نظر گرفته شده است. با استفاده از این سه مقایسهگر میزان سطح ولتاژ خروجی نسبت به ولتاژ مرجع، مشخص میشود. چنانچه سطح ولتاژ خروجی کمتر از حد بالای ولتاژ مرجع و بیشتر از حد پایین ولتاژ مرجع باشد، شمارندهی بالا-پایین شمار شروع به کار میکند و در غیر این صورت ثبات تقریب متوالی وارد عمل میشود. در این تثبیت کننده ولتاژ با استفاده از آرایهی PMOS، جریان بار خروجی، کنترل میشود و مقدار ولتاژ خروجی، به ولتاژ مرجع میرسد. با توجه به مدار پیشنهادی میزان فراجهش و فروجهش ولتاژ خروجی، کاهش مییابد که این امر باعث افزایش سرعت پاسخ گذرا میشود. در مدار پیشنهادی مقدار ولتاژ خروجی تثبیت شده نسبت به ولتاژ ورودی به اندازهی 100 میلیولت کاهش یافته است . مدار تثبیت کننده ولتاژ پیشنهادی در تکنولوژی 180 نانومتری CMOS طراحی و شبیه سازی شده است. مقدار ولتاژ ورودی برای مدار پیشنهادی برابر با 0/7 ولت و مقدار ولتاژ خروجی برابر با 0/6 ولت در نظر گرفته شده است.کليدواژه ها

تثبیت کنندهی ولتاژ با افت کم دیجیتالی، ثبات تقریب متوالی، شمارنده بالا-پایین شمارکد مقاله / لینک ثابت به این مقاله

برای لینک دهی به این مقاله، می توانید از لینک زیر استفاده نمایید. این لینک همیشه ثابت است :نحوه استناد به مقاله

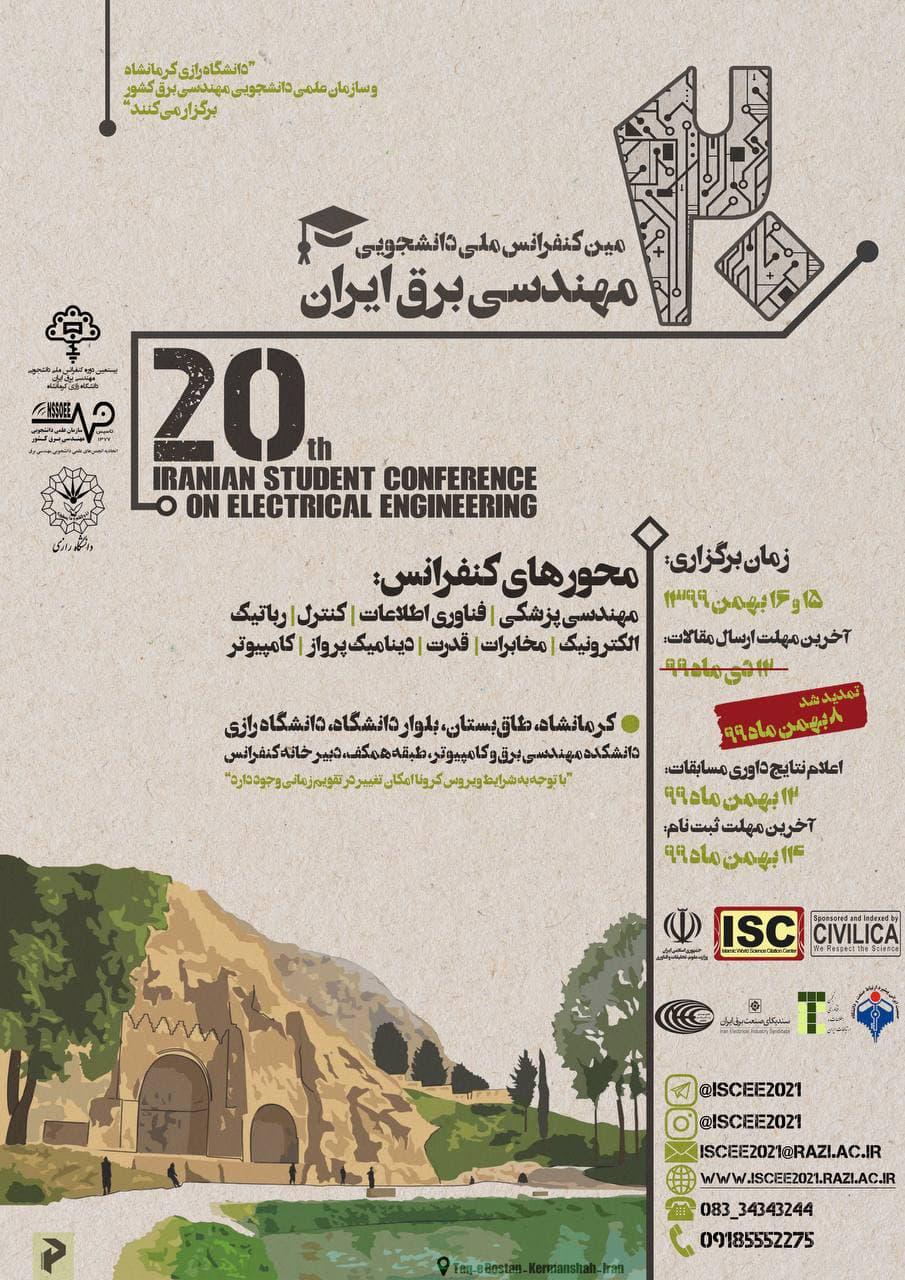

در صورتی که می خواهید در اثر پژوهشی خود به این مقاله ارجاع دهید، به سادگی می توانید از عبارت زیر در بخش منابع و مراجع استفاده نمایید:شهباز ریحانی , 1400 , طراحی تثبیت کننده ولتاژ با افت کم دیجیتالی با استفاده ازثبات تقریب متوالی ادغام شده با شمارندهی بالا-پایین شمار , بیستمین کنفرانس ملی دانشجویی مهندسی برق ایران

دیگر مقالات این رویداد

© کلیه حقوق متعلق به دانشگاه رازی کرمانشاه میباشد.